EPFL-TTO EPFL Innovation Park J CH-1015 Lausanne Switzerland +41 21 693 70 23 http://tto.epfl.ch/

Research Contact

Simone Frasca +41 78 722 09 43 simone.frasca@epfl.ch TTO Contact

Dr Mauro Lattuada +41 21 693 35 63 mauro.lattuada@epfl.ch

Licensing Opportunity

TTO - Technology Transfer Office

# Fabrication method to remove scalloping and tapering effects in through-silicon vias

Ref. Nr

6.2031

### Keywords

3D chip integration, Thoughsilicon vias, silicon fabrication, deep reactive etching, anisotropic etching.

Intellectual Property

Fabrication process step

Publications

S. Frasca et al., "The Michelangelo step: removing scalloping and tapering effects in high aspect ratio icon via Scientific Reports 11, 3997 (2021)

Date

18/02/2021

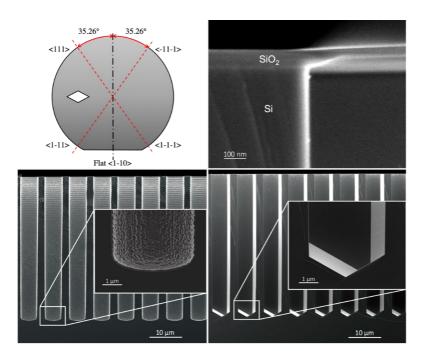

Effects of the Michelangelo Process on 5  $\mu m$  wide, 40  $\mu m$  deep through silicon vias. It appears evident that wall roughness is completely eliminated, as the effect of tapering along the depth of the via.

## Description

In the last 70 years, the continuous downscaling of semiconductor devices has offered increased device speed and density increases following Moore's prediction. However, as feature sizes got smaller, down to the current 7 nm (i.e. Intel, Samsung, TSMC), there is a physical limitation in scaling before entering the realm of quantum effects. The semiconductor community has shifted towards 3D integration to achieve higher electrical component density and increased performance.

In this context, TSVs are among major technology such infrastructures. players in modern high-volume manufacturing. However, the usual standardized TSV fabrication process has to deal with scalloping, an imperfection in the sidewalls caused by the deep reactive ion etching (DRIE). The presence of scalloping causes stress and field concentration in the dielectric barrier, thereby dramaticallv impacting the following TSV filling step, which is performed by means of electrochemical plating.

We propose here a new scallop free and non-tapered approach to overcome this challenge by adding a new step to the standard TSV procedure exploiting the crystalline orientation of silicon wafers.

## Advantages

Avoiding field concentration and allowing higher aspect ratio is a key aim for TSV fabrication. These aspects require extremely well calibrated processes and expensive machines to damp these effects down. Our approach is a quick and low-cost solution that allows to get better results without the need of

### Applications

- High quality, high-aspect ratio TSV fabrication for via-first, CMOS 3D integration.

- High quality TSVs for via-last for most non-CMOS fabrication processes.